# **COURSE DESCRIPTOR BOOKLET**

## **M.Tech**

## **ELECTRONICS AND COMMUNICATION ENGINEERING**

(Accredited by NBA)

## **R-16 REGULATIONS**

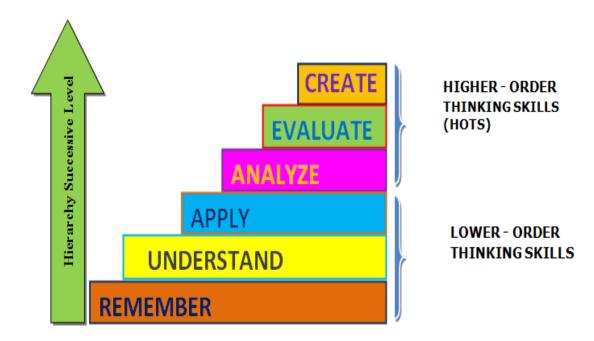

## **BLOOM'S TAXONOMY OF LEARNING OUTCOMES**

.....Moving Towards Perfection in Engineering

**INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous)

Approved by AICTE; Affiliated to JNTUH and Accredited by NAAC with 'A' Grade Dundigal, Hyderabad - 500 043

# Vision

To produce professionally competent Electronics and Communication Engineers capable of effectively and efficiently addressing the technical challenges with social responsibility.

# Mission

The mission of the Department is to provide an academic environment that will ensure high quality education, training and research by keeping the students abreast of latest developments in the field of Electronics and Communication Engineering aimed at promoting employability, leadership qualities with humanity, ethics, research aptitude and team spirit.

| S. No.                                         |                                                                                 | Page No. |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------|----------|--|--|--|

| PART – I<br>(As Per NBA Norms post June, 2015) |                                                                                 |          |  |  |  |

| 1                                              | Program Educational Objectives, Outcomes and Assessment Criteria                | 5        |  |  |  |

| 2                                              | M. Tech – Embedded systems Program Educational Objectives                       | 6        |  |  |  |

| 3                                              | M. Tech - Embedded systems Program Outcomes                                     | 8        |  |  |  |

| 4                                              | Mapping of Program Educational Objectives to Program Outcomes                   | 9        |  |  |  |

| 5                                              | Relation between the Program Outcomes and the Program Educational Objectives    | 10       |  |  |  |

| 6                                              | Program Outcomes of M.Tech, Embedded systems Masters.                           | 11       |  |  |  |

| 7                                              | Procedures for Outcome Delivery and Assessment with Respect to Program Outcomes | 13       |  |  |  |

| 8                                              | Methods of Measuring Learning Outcomes and Value Addition                       | 15       |  |  |  |

| Я                                              | PART – II<br>SSESSMENT OF COURSE LEVEL STUDENT LEARNING OUTC                    | OMES     |  |  |  |

| 1                                              | Course Purpose                                                                  | 20       |  |  |  |

| 2                                              | Expected Learning Outcomes                                                      | 21       |  |  |  |

| 3                                              | To Define Effective Learning Outcome Statements                                 | 21       |  |  |  |

| 4                                              | Tips for Developing Course Level Expected Learning Outcomes Statements          | 23       |  |  |  |

| 5                                              | Sample Expected Learning Outcomes Statements                                    | 23       |  |  |  |

| 6                                              | An Overview of Assessment                                                       | 24       |  |  |  |

| 7                                              | Description of a Course Purpose                                                 | 25       |  |  |  |

| 8                                              | Procedure for Development of Expected Learning Outcomes for a Course            | 26       |  |  |  |

| 9                                              | References                                                                      | 27       |  |  |  |

|                                                | ANNEXURES                                                                       |          |  |  |  |

| А                                              | Sample Course Description (As Per NBA Norms post June, 2015)                    | 28       |  |  |  |

### **Contents** Program Education Objectives and Outcomes

As Per NBA Norms Post June, 2016 Semester: I-I, I-II, II-I, II-II

# Part – I

#### PROGRAM EDUCATIONAL OBJECTIVES AND OUTCOMES

First version 22 July, 2014

## **Program Educational Objectives, Program Outcomes and Assessment Criteria** (Approved by DAC ECE on 3/9/2014):

**Electronics and Communication Engineering Department Advisory Council:** The Electronics and Communication Engineering Department Advisory Council (ECEDAC) includes a diverse group of experts from academic and industry, as well as alumni representation. The Advisory Board meets annually, or as needed, for a comprehensive review of the Electronics and Communication Engineering Department strategic planning and programs. The Advisory Council meets with administration, faculty and students and prepares a report, which is presented to principal. In each visit, the Department of Electronics and Communication Engineering responds to the report indicating improvements and amendments to the program.

## 1. PROGRAM EDUCATIONAL OBJECTIVES, OUTCOMES AND ASSESSMENT CRITERIA

#### Learning Outcomes, Assessment Criteria

The educational aims of a module are statements of the broad intentions of the teaching team. They indicate the objectives that the teaching team intends to cover and the learning opportunities that are necessary to be available to the student. A learning outcome is a statement that indicates the content that a learner (student) is expected to know, understand and/or be able to do at the end of a period of learning. It is advisable to express learning outcomes with the common prefix:

'On completion of (the period of learning e.g. module), the student is expected to be able to...'

Generally, learning outcomes do not specify curriculum, but more general areas of learning. It is not possible to prescribe precisely how specific a learning outcome statement should be. There is a balance to be struck between the degree of specificity in a learning outcome statement and that achieved by the assessment criteria. If there are too many learning outcomes for a module, then either they are becoming assessment criteria or they are specifying too much curricular detail. The curriculum should be described in the range statement. Too few learning outcomes are unlikely to provide sufficient information on the course. As a guide, there should be between 4 and 8 learning outcomes for a course.

The Program Educational Objectives (PEOs) of the Electronics and Communication Engineering department are broad statements or road maps describing career and professional objectives that intend the graduates to achieve through this program.

#### 2. M. TECH – EMBEDDED SYSTEMS PROGRAM

#### **EDUCATIONAL OBJECTIVES**

A graduate of Institute of Aeronautical Engineering in Embedded systems discipline should have a successful career in Electronics and Communication Engineering or a related field, and within three to five years, should attain the following:

#### **PROGRAM EDUCATIONAL OBJECTIVES:**

#### **PEO1.** Research and development

Be successful practicing professionals or pursue doctoral studies in allied areas, contributing significantly to **research and development** activities

#### **PEO2.** Demonstrate

**Demonstrate** technical competence, such as identifying, formulating, analyzing, and creating engineering solutions using appropriate current embedded engineering techniques, skills, and tools.

#### **PEO3.** Communicate

To work and **communicate** effectively in inter-disciplinary environment, either in a team or independently and establish leadership qualities.

#### **PEO4.** Apply

An ability to **apply** in-depth knowledge to evaluate, analyze and synthesize existing and novel designs.

These objectives are quite broad by intention, as Electronics and Communication Engineering graduates may seek further education or work in diverse areas. To make these objectives meaningful, they may be demonstrated by performance, actions, or achievements.

## i. To prepare the students who will be able to attain a solid foundation in Embedded systems fundamentals with an attitude to pursue continuing education.

- □ Make the students to understand their aptitude to choose the correct path of study which leads to higher qualifications and heights in the chosen field.

- □ Should be prepared to undergo rigorous training in their fields of working.

- □ Be capable of utilizing the solid foundation obtained at institute to apply successfully in solving the real time engineering problems.

- □ Students need to have creative thinking processes that are acquired through good training to find solutions to engineering problems.

- ii. To prepare the students to function professionally in an increasingly international and rapidly changing world due to the advances in technologies and concepts and to contribute to the needs of the society.

- Adoptability and accommodative mind set to suit modern world and changing economies.

- □ By working hard in the chosen field and sharing the professional experience at different forums within and outside the country.

- □ Desirable to be a member of various professional societies (IEEE, IETE, ISTE, IE, and etc.) to keep yourself abreast with the state-of-the-art technology.

- □ Should continue additional education in a broad range of subjects other than engineering may be needed in order to meet professional challenges efficiently and effectively.

- Continuous interaction with educational and research institutions or industrial research labs.

- □ Have a sound foundation of knowledge within a chosen field and achieve good depth and experience of practice in it.

- □ Able to relate knowledge within chosen field to larger problems in society and able to appreciate the interaction between science, technology, and society.

- □ Strong grasp of quantitative reasoning and an ability to manage complexity and ambiguity.

- □ To conduct research, and design, develop, test and oversee the development of electronic systems for global upliftment.

- □ Applying scientific knowledge to solve technical problems and develop products and services that benefit the society.

- □ An electronic engineer shall contribute to the society by research, design and development, testing and evaluation, application by manufacturing, maintenance by service, management and other functions like sales, customer service and etc.

# iii. To prepare the students to acquire and exercise excellent leadership qualities, at various levels appropriate to their experience, to address issues in a responsive, ethical, and innovative manner.

- Gives ample opportunity to work in diverse fields to acquire leadership roles in professional circles outside the workplace.

- □ Should keep in mind that the opportunities may change with the times.

- □ Should be prepared for creative solo and collaborative brainstorming sessions.

- □ Be able to inspire the team with selfless motivation and attitude to achieve success.

- □ Ability to think laterally or at-least have a flexibility of thought and make choices based on the requirement for situation.

## iv. To prepare the students who will be able to excel, in their careers by being a part of success and growth of an organization, with which they are associated.

- □ To achieve this, the focus should not be limited to an engineering curriculum and even to the class room.

- □ Continuing professional education by attending short term in courses design to update engineering skills.

- □ A lifelong commitment to learning new and specialized information.

- □ Should accept first person responsibility and should take the initiative in carrying out the work.

- □ Should be determined for the duty and dedicated to work and have passion for that.

- □ Be delight at work with a positive attitude.

- □ Should be a detailed worker so that one can be relied by the organization.

The department of Electronics and Communication Engineering periodically reviews these objectives and as part of this review process, encourages comments from all interested parties including current students, alumni, prospective students, faculty those who hire or admit our graduates to other programs members of related professional organizations, and colleagues from other educational institutions.

#### 3. M. TECH – EMBEDDED SYSTEMS PROGRAM OUTCOMES:

Masters of the embedded systems Program Outcomes will demonstrate:

#### **PROGRAM OUTCOMES:**

#### **PO1. Engineering Knowledge**

Apply advanced level knowledge, techniques, skills and modern tools in the field of Embedded Systems and sub areas IoT, Processor technology, and Storage technology.

#### **PO2. Teamwork and Project Management**

Function on multidisciplinary environments by working cooperatively, creatively and responsibly as a member of a team.

#### **PO3.** Develop and Novel Designs

Respond to global policy initiatives and meet the emerging challenges with sustainable technological solutions in the field of electronic product designing.

#### **PO4.** Analyze Complex Systems

Demonstrate the importance of embedded technologies and design new innovative products for solving society relevant problems.

#### **PO5.** Technical Presentation Skills

Write and present a substantial technical report / document.

#### **PO6.** Development of Solutions

Independently carry out research / investigation and development work to solve practical problems.

#### **PO7.** Lifelong learning

Recognize the need to engage in lifelong learning through continuing education and research.

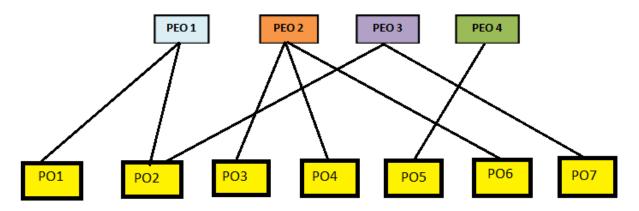

#### 4. MAPPING OF PROGRAM EDUCATIONAL OBJECTIVES TO PROGRAM OUTCOMES AND PROGRAM SPECIFIC OUTCOMES

The following Figure shows the correlation between the PEOs and the POs and PSOs

Figure: Correlation between the PEOs and the POs

| The following Table shows the correlation between the Program Educational Objectives a | nd the |

|----------------------------------------------------------------------------------------|--------|

| Program Outcomes & Program Specific Outcomes                                           |        |

|     | Program Educational Objectives                                                                                                                                              |     | Program Outcomes                                                                                                                                                                                               |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι   | Be successful practicing professionals or<br>pursue doctoral studies in allied areas,<br>contributing significantly to <b>research and</b><br><b>development</b> activities | PO1 | <b>Engineering Knowledge</b><br>Apply advanced level knowledge, techniques, skills<br>and modern tools in the field of Embedded Systems<br>and sub areas IoT, Processor technology, and Storage<br>technology. |

|     |                                                                                                                                                                             | PO2 | <b>Teamwork and Project Management</b><br>Function on multidisciplinary environments by<br>working cooperatively, creatively and responsibly as<br>a member of a team.                                         |

| II  | To be in a position to analyze real life<br>problems and design socially accepted and<br>economically feasible solutions in the<br>respective fields.                       | PO3 | <b>Develop and Novel Designs</b><br>Respond to global policy initiatives and meet the<br>emerging challenges with sustainable technological<br>solutions in the field of electronic product designing.         |

|     |                                                                                                                                                                             | PO4 | Analyze Complex Systems<br>Demonstrate the importance of embedded<br>technologies and design new innovative products<br>for solving society relevant problems.                                                 |

|     |                                                                                                                                                                             | PO6 | <b>Development of Solutions</b><br>Independently carry out research / investigation and development work to solve practical problems.                                                                          |

| III | To work and <b>communicate</b> effectively in inter-disciplinary environment, either                                                                                        | PO2 | <b>Teamwork and Project Management</b><br>Function on multidisciplinary environments by                                                                                                                        |

|    | independently or in a team, and establish leadership qualities.                                                     |     | working cooperatively, creatively and responsibly as a member of a team.                                                    |

|----|---------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                     | PO7 | <b>Lifelong learning</b><br>Recognize the need to engage in lifelong learning<br>through continuing education and research. |

| IV | An ability to <b>apply</b> in-depth knowledge to<br>evaluate, analyze and synthesize existing<br>and novel designs. |     | Technical Presentation Skills<br>Write and present a substantial technical report /<br>document.                            |

#### 5. RELATION BETWEEN THE PROGRAM OUTCOMES AND PROGRAM EDUCATIONAL OBJECTIVES

A broad relation between the Program Educational Objectives and the Program Outcomes is given in the following table:

| POs | PEOs                            | (1)<br>Research and<br>development | (2)<br>Demonstrate | (3)<br>Communicate | (4)<br>Apply |

|-----|---------------------------------|------------------------------------|--------------------|--------------------|--------------|

| PO1 | Engineering Knowledge           | - 3                                |                    |                    |              |

| PO2 | Teamwork and Project Management | 3                                  |                    | 1                  |              |

| PO3 | Develop and Novel Designs       |                                    | 3                  |                    |              |

| PO4 | Analyze Complex Systems         |                                    | 3                  |                    |              |

| PO5 | Technical Presentation Skills   |                                    |                    |                    | 3            |

| PO6 | Development of Solutions        |                                    | 3                  |                    |              |

| PO7 | Lifelong learning               |                                    |                    | 3                  |              |

Relationship between Program Outcomes and Program Educational Objectives Key: 3 = Highly 2 Medium; 1 = Low

#### 6. PROGRAM OUTCOMES OF (M.Tech) EMBEDDED SYSTEMS MASTERS

Masters from accredited programs must achieve the following learning outcomes, defined by broad areas of learning.

The outcomes are distributed within and among the courses within our curriculum, and our students are assessed for the achievement of these outcomes, as well as specific course learning objectives, through testing, surveys, and other faculty assessment instruments. Information obtained in these assessments is used in a short-term feedback and improvement loop.

Each Electronics and Communication Engineering student will demonstrate the following attributes by the time they masters:

#### **PO1. Engineering Knowledge**

Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems

Performance Criteria Definitions

- □ Identify the concepts and/or equations

- **D** Execute the solution using a logic and structured approach

- **□** Evaluate the solution of the problem

#### **PO2. Teamwork and Project Management**

Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments

Performance Criteria Definitions

- □ Awareness of global effects of the product / practice / event

- □ Understanding of economic factors

- Awareness of implications to society at large

#### **PO3.** Develop Novel designs

Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations

Performance Criteria Definitions

- **u** Use modern engineering tools for the system design, simulation and analysis

- □ Use software applications effectively to write technical reports and oral presentations

- □ Use modern equipment and instrumentation in the design process, analysis and troubleshooting

#### **PO4.** Analyze Complex Systems

Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions

Performance Criteria Definitions

- □ Identify problem/purpose

- □ Prepare hypothesis

- □ Outline procedure

- □ List materials and equipment

- □ Conduct experiment

- □ Record observations, data and results

- □ Perform analysis

- Document conclusions

#### **PO5.** Technical Presentation skills

Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions

Performance Criteria Definitions

- □ Use appropriate format and grammatical structure

- □ Create a well organized document

- □ Present the results appropriately

- **Demonstrate effective oral communication**

#### **PO6.** Development of Solutions

Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations

Performance Criteria Definitions

- □ Awareness of global effects of the product / practice / event

- □ Understanding of economic factors

- Awareness of implications to society at large

#### **PO7.** Life-long Learning

Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change

Performance Criteria Definitions

- □ Find relevant sources of information

- □ Participate in school or professional seminars

- Derticipate in students or professional associations

# I SEMESTER

## **INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous) Dundigal, Hyderabad -500 043

#### **ELECTRONICS AND COMMUNICATION ENGINEERING**

#### **COURSE DESCRIPTOR**

| Course Title          | Embed  | ded C                            |           |         |            |         |  |

|-----------------------|--------|----------------------------------|-----------|---------|------------|---------|--|

| Course Code           | BES00  | BES001                           |           |         |            |         |  |

| Programme             | M. Teo | ch                               |           |         |            |         |  |

| Semester              | Ι      | ECE                              |           |         |            |         |  |

| Course Type           | Core   |                                  |           |         |            |         |  |

| Regulation            | IARE - | R16                              |           |         |            |         |  |

|                       |        |                                  | Theory    |         | Pra        | ctical  |  |

| Course Structure      | Lectu  | ires                             | Tutorials | Credits | Laboratory | Credits |  |

|                       | 3      |                                  | -         | 3       | 3          | 2       |  |

| <b>Course Faculty</b> | Ms N.  | Ms N.Anusha, Assistant Professor |           |         |            |         |  |

#### I. COURSE OVERVIEW:

This course provides the basic knowledge over the programming and functionality of the embedded systems. Embedded C is most popular programming language in software field for developing electronic gadgets. Each processor used in electronic system is associated with embedded software. This plays a key role in performing specific function by the processor and all the device working is based on microcontroller that are programmed by embedded C.

#### II. COURSE PRE-REQUISITES:

| Level | Course Code | Semester | Prerequisites        | Credits |

|-------|-------------|----------|----------------------|---------|

| UG    | -           | -        | Computer programming | -       |

| UG    | -           | -        | Embedded systems     | -       |

#### **III. MARKSDISTRIBUTION:**

| Subject    | SEE Examination | CIAExamination | Total Marks |

|------------|-----------------|----------------|-------------|

| Embedded C | 70 Marks        | 30 Marks       | 100 Marks   |

#### IV. DELIVERY / INSTRUCTIONAL METHODOLOGIES:

| ~ | LCD / PPT              | ~ | Seminars | ~ | Videos | ~ | MOOCs |

|---|------------------------|---|----------|---|--------|---|-------|

| × | Open Ended Experiments |   |          |   |        |   |       |

#### V. EVALUATION METHODOLOGY:

The course will be evaluated for a total of 100 marks, with 30 marks for Continuous Internal Assessment (CIA) and 70 marks for Semester End Examination (SEE). Out of 30 marks allotted for CIA during the semester, marks are awarded by taking average of two CIA examinations.

**Semester End Examination (SEE):** The SEE is conducted for 70 marks of 3 hours duration. The syllabus for the theory courses is divided into five units and each unit carries equal weightage in terms of marks distribution. The question paper pattern is as follows. Two full questions with "either" or "choice" will be drawn from each unit. Each question carries 14 marks. There could be a maximum of two sub divisions in a question.

The emphasis on the questions is broadly based on the following criteria:

| 50 % | 6 To test the objectiveness of the concept.     |

|------|-------------------------------------------------|

| 30 % | 6 To test the analytical skill of the concept.  |

| 20 % | 6 To test the application skill of the concept. |

#### **Continuous Internal Assessment (CIA):**

CIA is conducted for a total of 30 marks (Table 1), with 25 marks for Continuous Internal Examination (CIE), 05 marks for Technical Seminar and Term Paper.

| Component          | Theory   |                                        |             |

|--------------------|----------|----------------------------------------|-------------|

| Type of Assessment | CIE Exam | Technical<br>Seminar and<br>Term Paper | Total Marks |

| CIA Marks          | 25       | 05                                     | 30          |

Table 1: Assessment pattern for CIA

#### **Continuous Internal Examination (CIE):**

Two CIE exams shall be conducted at the end of the 9<sup>th</sup> and 17<sup>th</sup> week of the semester respectively. The CIE exam is conducted for 25 marks of 2 hours duration, consisting of 5 one mark compulsory questions in part-A and 4 questions in part-B. The student has to answer any 4 questions out of five questions, each carries 5 marks. Marks are awarded by taking average of marks scored in two CIE exams.

#### **Technical Seminar and Term Paper:**

Two seminar presentations and the term paper with overview of topic are conducted during II semester. The evaluation of technical seminar and term paper is for maximum of 5 marks. Marks are awarded by taking average of marks scored in two Seminar Evaluations.

#### VI. HOW PROGRAM OUTCOMES ARE ASSESSED:

|      | Program Outcomes (POs)                                                                                                                                                 | Strength | Proficiency<br>assessed by |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------|

| PO 1 | Apply advanced level knowledge, techniques, skills and<br>modern tools in the field of embedded system and sub areas<br>IOT, Processor technology, storage technology. | 3        | Term paper,<br>Seminar     |

| PO 2 | Function on multidisciplinary environment by working<br>cooperatively, creatively and responsibly as a member of a<br>team.                                            | 3        | Term paper,<br>Seminar     |

| PO 3 | Respond to global policy initiatives and meet the emerging<br>challenges with sustainable technological solutions in the<br>field of electronics product designing.    | 2        | Term paper                 |

| PO 4 | Demonstrate the importance of embedded technologies and<br>design new innovative products for solving society relevant<br>problems                                     | 3        | Term paper,<br>Seminar     |

|      | Program Outcomes (POs)                               | Strength | Proficiency<br>assessed by |

|------|------------------------------------------------------|----------|----------------------------|

| PO 6 | Independently carry out research / investigation and | 3        | Term paper,                |

|      | development work to solve practical problems.        |          | Seminar                    |

|      | 3 = High; 2 = Medium; 1 = Low                        |          |                            |

#### VII. COURSE OBJECTIVES (COs):

| The course should enable the students to: |                                                                   |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------|--|--|--|

| Ι                                         | Understand embedded C and use it for programming embedded system. |  |  |  |

| II                                        | Apply techniques for data transfer between I/O ports and memory.  |  |  |  |

| III                                       | Apply object oriented programming for designing embedded system.  |  |  |  |

| IV                                        | Use timers to generate time delay.                                |  |  |  |

#### VIII. COURSE OUTCOMES (COs):

| COs  | Course Outcome                                                                                      | CLOs   | Course Learning Outcome                                       |

|------|-----------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------|

|      |                                                                                                     | CLO 1  | Understanding the basic concepts of<br>Embedded C             |

| CO 1 | Understand the basic knowledge<br>about embedded processor and<br>hardware and software interrupts. | CLO 2  | Understanding the basic concept of interfacing and interrupts |

|      | L                                                                                                   | CLO 3  | Understanding the basic of 8051 architecture                  |

|      |                                                                                                     | CLO 4  | Analyze the programming on switches                           |

| CO 2 | Understand the basic embedded<br>programming concepts in C and<br>assembly language                 | CLO 5  | Analysis of processor scheduling real time.                   |

|      |                                                                                                     | CLO 6  | Understanding the programming language tools.                 |

| CO 3 | Illustrate various tasks in real time operating systems including                                   | CLO 7  | Understanding the basic concepts of coding on embedded C.     |

| 05   | inter-task communication and software development tool                                              | CLO 8  | Applications of software on real time constraints             |

|      | Explore on various testing                                                                          | CLO 9  | Analyse the programming on real time constraints              |

| CO 4 | concepts on real time applications.                                                                 | CLO 10 | Understanding the testing concepts on real time applications  |

| CO 5 | Apply embedded programming                                                                          | CLO 11 | Understanding the basic concepts on software architecture     |

| CO 5 | concepts on case study.                                                                             | CLO 12 | Understanding the real time concepts using case study.        |

#### IX. COURSE LEARNING OUTCOMES (CLOs):

| CLO Code  | CLO's | At the end of the course, the student will<br>have the ability to: | PO's<br>Mapped | Strength of<br>Mapping |

|-----------|-------|--------------------------------------------------------------------|----------------|------------------------|

| BES001.01 | CLO 1 | Understanding the basic concepts of Embedded C.                    | PO1            | 2                      |

| BES001.02 | CLO 2 | Understanding the basic concept of interfacing and interrupts      | PO1, PO2       | 3                      |

| BES001.03 | CLO 3 | Understanding the basic of 8051 architecture                       | PO1, PO3       | 3                      |

| BES001.04 | CLO 4 | Analyse the programming on switches                                | PO4            | 3                      |

| BES001.05 | CLO 5 | Analysis of processor scheduling real time.                        | PO3, PO4       | 3                      |

| BES001.06 | CLO 6 | Understanding the programming language tools.                      | PO1, PO6       | 3                      |

| CLO Code  | CLO's  | At the end of the course, the student will<br>have the ability to: | PO's<br>Mapped | Strength of<br>Mapping |

|-----------|--------|--------------------------------------------------------------------|----------------|------------------------|

| BES001.07 | CLO 7  | Understanding the basic concepts of coding on embedded C.          | PO4            | 3                      |

| BES001.08 | CLO 8  | Applications of software on real time constraints                  | PO6            | 2                      |

| BES001.09 | CLO 9  | Analyse the programming on real time constraints                   | PO3, PO6       | 3                      |

| BES001.10 | CLO 10 | Understanding the testing concepts on real time applications       | PO3, PO4       | 3                      |

| BES001.11 | CLO 11 | Understanding the basic concepts on software architecture          | PO4            | 3                      |

| BES001.12 | CLO 12 | Understanding the real time concepts using case study              | PO2, PO3       | 2                      |

**3= High; 2 = Medium; 1 = Low**

# X. MAPPING COURSE OUTCOMES LEADING TO THE ACHIEVEMENTOF PROGRAM OUTCOMES

| <b>Course Outcomes</b> | Program Outcomes (PO) |      |      |      |             |  |  |

|------------------------|-----------------------|------|------|------|-------------|--|--|

| (COs)                  | <b>PO 1</b>           | PO 2 | PO 3 | PO 4 | <b>PO 6</b> |  |  |

| CO 1                   | 3                     | 3    | 3    |      |             |  |  |

| CO 2                   | 3                     |      | 2    | 3    | 2           |  |  |

| CO 3                   |                       |      |      | 3    | 3           |  |  |

| CO 4                   |                       |      | 2    | 3    | 3           |  |  |

| CO 5                   |                       | 3    | 3    | 2    |             |  |  |

**3= High; 2 = Medium; 1 = Low**

## XI. MAPPING COURSE LEARNING OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES

| Course Learning    |     | Program Outcomes |     |     |     |  |

|--------------------|-----|------------------|-----|-----|-----|--|

| Outcomes<br>(CLOs) | PO1 | PO2              | PO3 | PO4 | PO6 |  |

| CLO 1              | 2   |                  |     |     |     |  |

| CLO 2              | 3   | 3                |     |     |     |  |

| CLO 3              | 3   |                  | 3   |     |     |  |

| CLO 4              |     |                  |     | 3   |     |  |

| CLO 5              |     |                  | 3   | 3   |     |  |

| CLO 6              | 3   |                  |     |     | 3   |  |

| CLO 7              |     |                  |     | 3   |     |  |

| CLO 8              |     |                  |     |     | 2   |  |

| CLO 9              |     |                  | 3   |     | 3   |  |

| CLO 10             |     |                  | 3   | 3   |     |  |

| CLO 11             |     |                  |     | 3   |     |  |

| CLO 12             |     | 2                | 2   |     |     |  |

#### XII. ASSESSMENT METHODOLOGIES-DIRECT

| CIE Exams               | PO1,PO2, PO3,<br>PO4, PO6 | SEE Exams | PO1, PO2, PO3,<br>PO4, PO6 | Seminarand<br>Term Paper | PO1, PO2, PO3,<br>PO4, PO6 |

|-------------------------|---------------------------|-----------|----------------------------|--------------------------|----------------------------|

| Laboratory<br>Practices | -                         | Viva      | -                          | Mini Project             | -                          |

#### XIII. ASSESSMENT METHODOLOGIES-INDIRECT

| ~ | Early Semester Feedback                | ~ | End Semester OBE Feedback |

|---|----------------------------------------|---|---------------------------|

| ~ | Assessment of Mini Projects by Experts |   |                           |

#### XIV. SYLLABUS

#### UNIT-I

#### PROGRAMMING EMBEDDED SYSTEMS IN C

Introduction, what is an embedded system, which processor should you use, which programming language should you use, which operating system should you use, how do you develop embedded software, conclusions; Introduction, what's in a name, the external interface of the standard 8051, reset requirements, clock frequency and performance, memory issues, I/O pins, timers, interrupts, serial interface, power consumption ,conclusions.

## UNIT-II

#### SWITCHES

Introduction, basic techniques for reading from port pins; Example: Reading and writing bytes, example: Reading and writing bits (simple version), Example: Reading and writing bits (generic version), The need for pull-up resistors, Dealing with switch bounce, Example: Reading switch inputs (basic code), example: counting goats, conclusions.

#### UNIT-III

#### ADDING STRUCTURE TO THE CODE

Introduction, object oriented programming with C, the project header (MAIN.H), the port header (PORT.H); Example: Restructuring the "Hello Embedded World" example, Example: Restructuring the goat-counting example, further examples and conclusions.

#### UNIT-IV

#### MEETING REAL-TIME CONSTRAINTS

Introduction, creating hardware delays using Timer 0 and Timer 1, example: Generating a precise 50 ms delay, example: Creating a portable hardware delay, Why not use Timer 2? The need for timeout mechanisms, creating loop timeouts and example: Testing loop timeouts, example: A more reliable switch interface, Creating hardware timeouts, example: Testing a hardware timeout, conclusions.

#### UNIT-V

#### CASE STUDY: INTRUDER ALARM SYSTEM

Introduction, The software architecture, key software components used in this example, running the program, the software, conclusions.

#### **Text Books:**

1. Michael J. Pont, "Embedded C", Pearson Education, 2<sup>nd</sup> Edition, 2008.

#### **Reference:**

1.Nigel Gardner, "The Microchip PIC in CCS C", Ccs Inc, 2<sup>nd</sup>Revision Edition, 2002.

**Reference E-Text Books:**

1. http://www.keil.com/forum/5973/

- 2. http://nptel.ac.in/courses/Webcourse,contents/IIT%20Kharagpur/Embedded%20systems/New

3. http://nptel.iitg.ernet.in/courses/Elec\_Engg/IIT%20Delhi/Embedded%20Systems%20(Video).htm

- 4. http://freevideolectures.com/Course/2999/Embedded-Systems-I/5

#### XV. **COURSE PLAN:**

The course plan is meant as a guideline. Probably there may be changes.

| Lecture<br>No | Topic Outcomes                                                              | Topic/s to be covered                                                                                                                                                                                                                                            | Reference           |

|---------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1-3           | Understand the concepts of embedded system.                                 | Introduction, what is an embedded system                                                                                                                                                                                                                         | T1:1.1, 1.2         |

| 4-6           | Understand the concepts of operating system.                                | which processor should you use, which programming language should you use                                                                                                                                                                                        | T1:2.1              |

| 7-9           | Design the programming on embedded system                                   | which operating system should you use how do you develop embedded software                                                                                                                                                                                       | T1:2.2, 2.3         |

| 10-13         | Understand the standard the concepts of 8051                                | key software components used in this<br>example he external interface of the standard<br>8051                                                                                                                                                                    | T1:4.1,<br>4.2, 4.3 |

| 14-16         | Analyze the clock functions and I/O                                         | reset requirements, clock frequency and<br>performancememory issues, I/O pins, timers,<br>interrupts                                                                                                                                                             | T1:4.2, 4.4         |

| 17-20         | Analyze the concepts of interface<br>and port pins                          | serial interface, power consumption,<br>conclusions<br>Introduction, basic techniques for reading from<br>port pins                                                                                                                                              | T1: 5.1,<br>5.2     |

| 21-22         | Design the example programming<br>and basic concepts of pull-up<br>resistor | Example programs on Reading and writing<br>bytes, Reading and writing bits simple<br>versionReading and writing bits, The need<br>for pull-up resistors                                                                                                          | T1:6.1,<br>6.2, 6.4 |

| 23-27         | Understand the basic of switch<br>and c programming                         | Dealing with switch bounce, Example:<br>Reading switch inputs (basic<br>code)Introduction, object oriented<br>programming with Cthe project header<br>(MAIN.H), the port header (PORT.H);                                                                        | T1:7.2,<br>7.3, 7.4 |

| 28-36         | Design the example programming on goat counting                             | Restructuring the Hello Embedded World<br>Restructuring the goat-counting example,<br>further examples and conclusions                                                                                                                                           | T1:8.1, 8.3         |

| 37-40         | Understand the basic concepts of timer and testing the hardware.            | Introduction, creating hardware delays using<br>Timer 0 and Timer 1, Generating a precise 50<br>ms delay, example: Creating a portable<br>hardware delay, Why not use Timer 2<br>Creating hardware timeouts, example:<br>Testing a hardware timeout, conclusions | T1:5.3              |

| 41-45         | Understand the basic concepts of software architecture.                     | Introduction, The software architecture key software components used in this example                                                                                                                                                                             | T1:5.5,<br>5.6, 5.7 |

#### XVI. GAPS IN THE SYLLABUS-TO MEET INDUSTRY / PROFESSIONAL REQUIREMENTS:

| S No | Description                                 | Proposed Actions                   | <b>Relevance with POs</b> |

|------|---------------------------------------------|------------------------------------|---------------------------|

| 1    | Real time programming software architecture | Seminars / Guest Lectures / NPTEL  | PO 1, PO 4, PO 3          |

| 2    | Design concepts of embedded c               | Work Shops/ Guest Lectures / NPTEL | PO 6, PO 2                |

**Prepared by:** Mrs. Anusha. N, Assistant Professor

(Autonomous) Dundigal, Hyderabad -500 043

#### **ELECTRONICS AND COMMUNICATION ENGINEERING**

#### **COURSE DESCRIPTOR**

| Course Title     | WIRELESS LANS AND PANS              |           |            |         |  |  |

|------------------|-------------------------------------|-----------|------------|---------|--|--|

| Course Code      | BES002                              |           |            |         |  |  |

| Programme        | M.Tech                              |           |            |         |  |  |

| Semester         | Ι                                   |           |            |         |  |  |

| Course Type      | Elective                            |           |            |         |  |  |

| Regulation       | IARE - R16                          |           |            |         |  |  |

|                  | The                                 | eory      | Prac       | tical   |  |  |

| Course Structure | Lectures                            | Tutorials | Practicals | Credits |  |  |

|                  | 3                                   | -         | -          | 3       |  |  |

| Course Faculty   | Mrs. M Kalyani, Assistant Professor |           |            |         |  |  |

#### I. COURSE OVERVIEW:

Embedded systems have become the next inevitable wave of technology, finding application in diverse fields of engineering. The goal of this course is to impart training to graduate engineers, in specialized area of Embedded Systems so that they can develop expertise in developing and deploying embedded systems over a wide range of applications. This course provides the basic knowledge over the hardware units and devices for design of embedded systems. It also provides the information about the Use architectures of embedded RISC processors and system on chip processor design of embedded systems. This course is intended to Analyze interrupt latency, context switching time, for development of device drives for timing devices.

#### **II. COURSE PRE-REQUISITES:**

| Level | Course Code | Semester | Prerequisites                       | Credits |

|-------|-------------|----------|-------------------------------------|---------|

| UG    |             |          | Wireless Communication and Networks |         |

#### **III. MARKSDISTRIBUTION**

| Subject                | SEE Examination | CIA Examination | Total Marks |

|------------------------|-----------------|-----------------|-------------|

| Wireless LANs and PANs | 70 Marks        | 30 Marks        | 100         |

#### IV. DELIVERY / INSTRUCTIONAL METHODOLOGIES:

| ~ | LCD / PPT              | ~ | Seminars | ~ | Videos | ~ | MOOCs |

|---|------------------------|---|----------|---|--------|---|-------|

| × | Open Ended Experiments |   |          |   |        |   |       |

#### V. EVALUATION METHODOLOGY:

The course will be evaluated for a total of 100 marks, with 30 marks for Continuous Internal Assessment (CIA) and 70 marks for Semester End Examination (SEE). Out of 30 marks allotted for CIA during the semester, marks are awarded by taking average of two CIA examinations.

**Semester End Examination (SEE):** The SEE is conducted for 70 marks of 3 hours duration. The syllabus for the theory courses is divided into five units and each unit carries equal weightage in terms of marks distribution. The question paper pattern is as follows. Two full questions with "either" or "choice" will be drawn from each unit. Each question carries 14 marks. There could be a maximum of two sub divisions in a question.

The emphasis on the questions is broadly based on the following criteria:

| 50 % | To test the objectiveness of the concept.     |  |  |  |

|------|-----------------------------------------------|--|--|--|

| 30 % | To test the analytical skill of the concept.  |  |  |  |

| 20 % | To test the application skill of the concept. |  |  |  |

#### **Continuous Internal Assessment (CIA):**

CIA is conducted for a total of 30 marks (Table 1), with 25 marks for Continuous Internal Examination (CIE), 05 marks for Technical Seminar and Term Paper.

| Component          | The      |                                     |             |

|--------------------|----------|-------------------------------------|-------------|

| Type of Assessment | CIE Exam | Technical Seminar<br>and Term Paper | Total Marks |

| CIA Marks          | 25       | 05                                  | 30          |

Table 1: Assessment pattern for CIA

#### **Continuous Internal Examination (CIE):**

Two CIE exams shall be conducted at the end of the 9<sup>th</sup> and 17<sup>th</sup> week of the semester respectively. The CIE exam is conducted for 25 marks of 2 hours duration, consisting of 5 one mark compulsory questions in part-A and 4 questions in part-B. The student has to answer any 4 questions out of five questions, each carries 5 marks. Marks are awarded by taking average of marks scored in two CIE exams.

#### **Technical Seminar and Term Paper:**

Two seminar presentations and the term paper with overview of topic are conducted during II semester. The evaluation of technical seminar and term paper is for maximum of 5 marks. Marks are awarded by taking average of marks scored in two Seminar Evaluations.

#### VI. HOW PROGRAM OUTCOMES ARE ASSESSED:

|      | Program Outcomes (POs)                                                                                                                                                 | Strength | Proficiency<br>assessed by             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|

| PO 1 | Apply advanced level knowledge, techniques, skills and<br>modern tools in the field of embedded system and sub areas<br>IoT, Processor technology, storage technology. | 3        | Term paper                             |

| PO 2 | Function on multidisciplinary environments by working<br>cooperatively, creatively and responsibly as a member of a<br>team.                                           | 2        | Term paper and Guest Lectures          |

| PO 3 | Respond to global policy initiatives and meet the emerging<br>challenges with sustainable technological solutions in the<br>field of electronic product designing.     | 3        | Seminar and<br>Guest Lectures          |

| PO 6 | Independently carry out research / investigation and development work to solve practical problems.                                                                     | 3        | NPTEL Videos<br>and Guest<br>Lecturers |

**3** = High; **2** = Medium; **1** = Low

#### VII. COURSE OBJECTIVES:

| Ι   | Understand different WLAN topologies and transmission techniques. |  |  |  |

|-----|-------------------------------------------------------------------|--|--|--|

| II  | Interpret Bluetooth and Zigbee technologies.                      |  |  |  |

| III | Enhance the understanding of 3G systems and 4G networks.          |  |  |  |

#### VIII. COURSE OUTCOMES (COs):

| COs  | <b>Course Outcome</b>                                                             | CLOs   | Course Learning Outcome                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO 1 | Describefirst and second generation cellular systems and                          | CLO 1  | Understand and analyze first and second generation cellular systems.                                                                                                                          |

|      | analyze cellular communications from 1G to 3G.                                    | CLO 2  | Analyze cellular communications from 1G to 3G.                                                                                                                                                |

|      |                                                                                   |        | Explain wireless 4G systems, and wireless spectrum.                                                                                                                                           |

| CO 2 | Understand and analyze WLAN<br>topologies and analyze<br>transmission techniques. | CLO 4  | Describe carrier sense multiple access<br>(CSMA), carrier sense multiple access with<br>collision detection (CSMA/CD), carrier<br>sense multiple access with collision<br>avoidance(CSMA/CA). |

|      |                                                                                   | CLO 5  | Explain WLAN topologies and analyze transmission techniques                                                                                                                                   |

|      |                                                                                   | CLO 6  | Distinguish random access methods.                                                                                                                                                            |

| CO 3 | Demonstrate network<br>architecture and analyze MAC                               | CLO 7  | Describe importance of MAC layer applications                                                                                                                                                 |

|      | layer issues and describe the importance of MAC layer applications.               | CLO 8  | Explain network architecture and analyze MAC layer issues.                                                                                                                                    |

| CO 4 | Explore Bluetooth technology and Bluetooth specifications,                        | CLO 9  | Describe the importance of wireless private area networks.                                                                                                                                    |

|      | describe the importance of wireless private area networks.                        | CLO 10 | Explain Bluetooth technology and Bluetooth specifications.                                                                                                                                    |

|      |                                                                                   |        | Analyze Enhancements to Bluetooth technology and applications                                                                                                                                 |

| CO 5 | Develop practical skills in the use of ZigBee components and                      | CLO 12 | Describe IEEE 802.15.3, The IEEE 802.15.4                                                                                                                                                     |

|      | network topologies.                                                               | CLO 13 | Understand ZigBee components and network topologies.                                                                                                                                          |

|      |                                                                                   | CLO 14 | Analyze Device architecture and network topologies                                                                                                                                            |

#### IX. COURSE LEARNING OUTCOMES(CLOs):

| CLO<br>Code | CLO's | At the end of the course, the student will have the ability to | PO's<br>Mapped | Strength<br>of Mapping |

|-------------|-------|----------------------------------------------------------------|----------------|------------------------|

| BES002.01   | CLO 1 | Understand and Analyze First and                               | PO 1           | 2                      |

|             |       | Second Generation Cellular Systems.                            |                |                        |

| BES002.02   | CLO 2 | Analyze Cellular Communications from                           | PO 1, PO 2     | 2                      |

|             |       | 1G to 3G.                                                      |                |                        |

| BES002.03   | CLO 3 | Explain Wireless 4G systems, The                               | PO 1, PO 3     | 1                      |

|             |       | Wireless Spectrum.                                             |                |                        |

| BES002.04   | CLO 4 | Describe Carrier Sense Multiple                                | PO 2, PO 3     | 3                      |

|             |       | Access (CSMA), Carrier Sense Multiple                          |                |                        |

|            |        |                                           | 1          |   |

|------------|--------|-------------------------------------------|------------|---|

|            |        | Access with Collision Detection           |            |   |

|            |        | (CSMA/CD), Carrier Sense Multiple         |            |   |

|            |        | Access with Collision Avoidance           |            |   |

|            |        | (CSMA/CA).                                |            |   |

| BES002.05  | CLO 5  | Explain WLAN Topologies and Analyze       | PO 1       | 3 |

|            |        | Transmission Techniques                   |            |   |

| BES002.06  | CLO 6  | Distinguish Random Access Methods.        | PO 1       | 3 |

|            |        |                                           |            |   |

| BES002.07  | CLO 7  | Describe importance of Wireless Local     | PO 3       | 3 |

|            |        | Area Networks.                            |            |   |

| BES002.08  | CLO 8  | Explain Network Architecture and          | PO 1, PO 3 | 2 |

|            |        | Analyze MAC Layer issues.                 |            |   |

| BES002.09  | CLO 9  | Describe importance of Wireless Private   | PO 3, PO 6 | 2 |

|            |        | Area Networks.                            |            |   |

| BES002.10  | CLO10  | Explain Bluetooth technology and          | PO 1, PO 6 | 3 |

|            |        | Bluetooth specifications.                 |            |   |

| BES002.11  | CLO 11 | Analyze Enhancements to Bluetooth         | PO 2       | 2 |

|            |        | technology and applications               |            |   |

| BES002.12  | CLO 12 | Describe IEEE 802.15.3, The IEEE 802.15.4 | PO 2, PO 6 | 3 |

|            |        | Describe IEEE 802.13.5, The IEEE 802.15.4 |            |   |

| BES002.13  | CLO 13 | Understand ZigBee components and          | PO 2       | 2 |

|            |        | network topologies.                       |            |   |

| BES002.14  | CLO 14 | Analyze Device architecture and network   | PO 3, PO 6 | 3 |

|            |        | topologies                                |            |   |

| <b>A T</b> |        | Madiuma 1 Lawy                            |            |   |

3 = High; 2 = Medium; 1 = Low2

# X. MAPPING COURSE OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES:

| Course Outcomes |      | Dutcomes(PO) |      |             |  |

|-----------------|------|--------------|------|-------------|--|

| (COs)           | PO 1 | PO 2         | PO 3 | <b>PO 6</b> |  |

| CO 1            | 3    | 2            | 2    |             |  |

| CO 2            | 3    | 3            | 3    |             |  |

| CO 3            | 2    |              | 3    |             |  |

| CO 4            | 3    | 2            | 3    | 2           |  |

| CO 5            |      | 2            | 3    | 3           |  |

#### XI. MAPPING COURSE LEARNING OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES

| Course Learning    | Program Outcome(PO) |      |             |             |  |  |

|--------------------|---------------------|------|-------------|-------------|--|--|

| Outcomes<br>(CLOs) | <b>PO 1</b>         | PO 2 | <b>PO 3</b> | <b>PO 6</b> |  |  |

| CLO 1              | 3                   |      |             |             |  |  |

| CLO 2              | 3                   | 2    |             |             |  |  |

| CLO 3              | 3                   |      | 3           |             |  |  |

| CLO 4              |                     | 3    | 2           |             |  |  |

| CLO 5  | 2 |   |   |   |

|--------|---|---|---|---|

| CLO 6  | 2 |   |   |   |

| CLO 7  |   |   | 3 |   |

| CLO 8  | 2 |   | 3 |   |

| CLO 9  |   |   | 3 | 3 |

| CLO 10 | 3 |   |   | 3 |

| CLO 11 |   | 2 |   |   |

| CLO 12 |   | 2 |   | 3 |

| CLO 13 |   | 2 |   |   |

| CLO 14 |   |   | 2 | 3 |

#### **3** = High; **2** = Medium; **1** = Low

#### XII. ASSESSMENT METHODOLOGIES – DIRECT

| CIE Exams | PO1, PO2,<br>PO3, PO 6 | SEE Exams    | PO1, PO2,<br>PO3, PO 6 | Seminar and<br>Term Paper | PO1, PO2,<br>PO3, PO6 |

|-----------|------------------------|--------------|------------------------|---------------------------|-----------------------|

| Viva      | -                      | Mini Project | -                      | Laboratory<br>Practices   | -                     |

#### XIII. ASSESSMENT METHODOLOGIES -INDIRECT

| ~ | Early Semester Feedback                | > | End Semester OBE Feedback |

|---|----------------------------------------|---|---------------------------|

| × | Assessment of Mini Projects by Experts |   |                           |

#### **XIV. SYLLABUS:**

#### UNIT I WIRELESS SYSTEM&RANDOM ACCESS PROTOCOLS Introduction, First and Second Generation Cellular Systems, Cellular Communications from 1G to3G, Wireless 4G systems, The Wireless Spectrum; Random Access Methods: Pure ALOHA, Slotted ALOHA, Carrier Sense Multiple Access (CSMA), Carrier Sense Multiple Access with Collision Detection (CSMA/CD), Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA).. UNIT II WIRELESS LANS Introduction, importance of Wireless LANs, WLAN Topologies, Transmission Techniques: Wired Networks, Wireless Networks, comparison of wired and Wireless LANs; WLAN Technologies: Infrared technology, UHF narrowband technology, Spread Spectrum technology. UNIT III THE IEEE 802.11 STANDARD FOR WIRELESS LANS Network Architecture, Physical layer, The Medium Access Control Layer; MAC Layer issues: Hidden Terminal Problem, Reliability, Collision avoidance, Congestion avoidance, Congestion control, Security, The IEEE 802.11e MAC protocol.. UNIT IV WIRELESS PANS Introduction, importance of Wireless PANs, The Bluetooth technology: history and applications, technical overview, the Bluetooth specifications, piconet synchronization and Bluetooth clocks, Master-Slave Switch; Bluetooth security; Enhancements to Bluetooth: Bluetooth interference issues, Intra and Inter Piconet scheduling, Bridge selection, Traffic Engineering, QoS and Dynamics Slot Assignment, Scatter net formation.

#### UNIT V

#### THE IEEE 802.15 WORKING GROUP FOR WPANS

The IEEE 802.15.3, The IEEE 802.15.4, ZigBee Technology, ZigBee components and network topologies, The IEEE 802.15.4 LR-WPAN Device architecture: Physical Layer, Data Link Layer, The Network Layer, Applications; IEEE 802.15.3a Ultra wideband..

#### **TEXT BOOKS:**

- 1. Carlos de Morais Cordeiro, Dharma Prakash Agrawal, "AdHoc and Sensor Networks", World Scientific, 2011.

- 2. Vijay K.Garg, "Wireless Communications and Networking", Morgan Kaufmann Publishers, 2009.

**REFERENCES:**

KavehPahlaram, Prashant Krishnamurthy, "Wireless Networks", PHI, 2002.

Marks Ciampor, Jeorge Olenewa, "Wireless Communication", Cengage Learning, 2007.

#### **XV. COURSE PLAN:**

The course plan is meant as a guideline. There may probably be changes.

| Lecture<br>No | Topic Outcomes                                                                                                                                                                                                | Topic/s to be covered                                                                                                                                                                                                                        | Reference                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 1-3           | Understand and analyze<br>first and second<br>generation cellular<br>systems.                                                                                                                                 | Introduction, first and second generation<br>cellular systems, Cellular communications<br>from 1G to3G<br>Wireless 4G systems, The wireless<br>Spectrum                                                                                      | T1: 5.1,<br>T1: 5.2,<br>R1: 1.7                                  |

| 4-6           | Analyze Cellular<br>Communications from<br>1G to 3G.                                                                                                                                                          | Random Access Methods: Pure ALOHA,<br>Slotted ALOHA, Carrier Sense Multiple<br>Access (CSMA), Carrier Sense Multiple<br>Access with Collision Detection<br>(CSMA/CD), Carrier Sense Multiple<br>Access with Collision Avoidance<br>(CSMA/CA) | T1:6.1-<br>6.2, T1:<br>6.3, T1:<br>6.4-6.6                       |

| 7-9           | Explain Wireless 4G<br>systems, The Wireless<br>Spectrum.                                                                                                                                                     | Introduction, importance of Wireless<br>LANs, WLAN Topologies, Transmission<br>Techniques: Wired Networks,<br>Transmission Techniques: Wireless<br>Networks                                                                                  | T1:6.4-<br>6.6,<br>T1:6.7-<br>6.8, T1:<br>6.15<br>R2:7.1,<br>8.1 |

| 10-13         | Describe Carrier<br>Sense Multiple Access<br>(CSMA), Carrier Sense<br>Multiple Access with<br>Collision Detection<br>(CSMA/CD), Carrier<br>Sense Multiple Access<br>with Collision<br>Avoidance<br>(CSMA/CA). | comparison of wired and Wireless LANs,<br>WLAN Technologies: Infrared<br>technology, UHF narrowband technology                                                                                                                               | T1:7.1,<br>7.4<br>T1:7.7,<br>T1: 7.8-<br>7.10<br>R2:7.2          |

| 14-16         | Explain WLAN<br>Topologies and analyze<br>transmission techniques                                                                                                                                             | Spread Spectrum technology, Network<br>Architecture, Physical layer, The Medium<br>access control layer                                                                                                                                      | T1: 6.12,<br>T1: 9.4,<br>R2: 4.2,<br>T1: 9.6                     |

| 17-20         | Describe importance of<br>Wireless Local Area<br>Networks.                                                                                                                                                    | MAC Layer issues: Hidden terminal<br>problem, Reliability, Collision avoidance,<br>congestion avoidance, Congestion control                                                                                                                  | T1: 7.12,<br>T1: 10.4,<br>R2: 4.2,<br>T1: 10.6                   |

| 21-22         | Explain Network<br>architecture and analyze<br>MAC layer issues.                                                                                                                                              | Security, The IEEE 802.11e MAC protocol.<br>The IEEE 802.11e MAC protocol.<br>Introduction, importance of wireless PANs,<br>the Bluetooth technology: history and<br>applications                                                            | T1: 10.5,<br>T1: 8.1<br>T1: 8.4,<br>T1: 8.2,<br>T1:8.5,T1        |

| Lecture<br>No | Topic Outcomes                                                      | Topic/s to be covered                                                                                                                                    | Reference                            |

|---------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|               |                                                                     |                                                                                                                                                          | :8.6<br>R2: 4.4                      |

| 23-27         | Describe importance of<br>Wireless Private Area<br>Networks.        | Technical overview, the Bluetooth<br>specifications, piconet synchronization and<br>Bluetooth clocks, Master-Slave Switch,<br>Bluetooth security         | T1: 8.2<br>R2: 4.4,<br>T1: 8.9       |

| 28-36         | Explain Bluetooth<br>technology and<br>Bluetooth<br>specifications. | Enhancements to Bluetooth: Bluetooth<br>interference issues, Intra and Inter Piconet<br>scheduling, Bridge selection, Traffic<br>Engineering,            | T1: 8.12-<br>8.13, T1:<br>8.14       |

| 37-40         | Analyze Enhancements<br>to Bluetooth                                | QoS and Dynamics Slot Assignment,<br>Scatter net formation., The IEEE 802.15.3,<br>The IEEE 802.15.4, ZigBee components<br>and network topologies        | T1: 9.1,<br>T1: 9.2,<br>T1: 9.3      |

| 41-45         | Describe IEEE 802.15.3,<br>The IEEE 802.15.4                        | The IEEE 802.15.4 LR-WPAN device<br>architecture, physical layer, data link layer,<br>the network layer, applications, IEEE<br>802.15.3a ultra wideband. | R1:7.1-<br>7.3,<br>R1:7.4,<br>R1:7.7 |

# XVI. GAPS IN THE SYLLABUS - TO MEET INDUSTRY / PROFESSIONAL REQUIREMENTS:

| S No | Description                  | Proposed Actions                      | Relevance with<br>POs |

|------|------------------------------|---------------------------------------|-----------------------|

| 1    | Currently available Wireless | Seminars / Guest Lectures / NPTEL     | PO 1, PO 2,           |

|      | Communication and Networks   |                                       | PO 6                  |

| 2    | Interfacing Modules          | Work Shops/ Guest Lectures /<br>NPTEL | PO 2, PO 6            |

Prepared By: Ms. M Kalyani, Assistant Professor

HOD, ECE

**INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous) Dundigal, Hyderabad -500 043

#### **ELECTRONICS AND COMMUNICATION ENGINEERING**

#### **COURSE DESCRIPTOR**

| Course Title        | COM   | COMPUTER ARCHITECTURE                    |           |         |            |         |

|---------------------|-------|------------------------------------------|-----------|---------|------------|---------|

| Course Code         | BESO  | 03                                       |           |         |            |         |

| Programme           | M.Teo | ch                                       |           |         |            |         |

| Semester            | Ι     | I ECE                                    |           |         |            |         |

| Course Type         | Core  | Core                                     |           |         |            |         |

| Regulation          | IARE  | - R16                                    |           |         |            |         |

|                     |       |                                          | Theory    |         | Pra        | actical |

| Course<br>Structure | Lec   | tures                                    | Tutorials | Credits | Practicals | Credits |

|                     |       | 3                                        | -         | 3       | -          | -       |

| Course Faculty      | Mr. N | Ar. N Bhargav Kumar, Assistant Professor |           |         |            |         |

#### I. COURSE OVERVIEW: